It's been a busy weekend, so I'm splitting this update into several posts.

One of my goals for the weekend was to figure out how to best use the hot air soldering station I borrowed from work. I've watched a number of videos on YouTube on the topic, and while many are fun to watch, none that I saw gave specifics for temperature or flow rates. Fortunately I have a collection of dead and useless boards chock full of SMDs to experiment with.

First I experimented with de-soldering a bunch of 0603 resistors and capacitors. I learned that they often stay stuck to the board when they're already loose and can be lifted off with no effort. That was a surprise. I played with the flow rates to see how high I could go before the loose 0603s would blow around sitting loose on the bench. I duplicated a SparkFun video where I unsoldered a medium sized TQFP with no mechanical damage. This was fun -- I gotta get one of these things!

Finally I experimented with re-soldering the loose 0603s using solder paste. I've done this before with wire solder, but using paste was a new experience. The stuff comes out of the syringe looking like a gelatinous ooze, speckled with little solder balls. I was expecting it to adhere to the board, like toothpaste, but this stuff (Chip-Quik SMD291AX) slithers around, floating on the flux in the suspension, making it hard to distribute evenly. This is not what I expected, given what I'd seen in the videos. My first attempts resulted in way too much solder in some areas, leaving bridges and causing components to shift badly. Eventually I tried squeezing out a blob of solder paste on a convenient surface, and using a pointy tool to transfer small quantities by dipping the tip in the paste and then dabbing it onto the pads. Keeping the hot air flow rate down avoided blowing the components away and they ended up soldered very nicely.

I got stainless-steel solder stencils with my boards, but I was unsure if I'd use them. I want to build up and test the board in sections, rather than laying everything down at once, which would make it difficult to use the stencils. I decided to start with the two 2-bit counters on the far right side of the board. This would also require the circuits that generate the INH and ~INH signals, which are also on the far right side. I put the board flat on my bench, carefully aligned the stencil, and clamped it in place. I squeezed some solder paste onto the stencil and used an old credit card to squeegee it over the holes. It looked good when I lifted the stencil, but through the microscope it looked like gelatinous blobs rather than the rectangular blocks I expected. Some of the blobs had spread enough to form larger blobs bridging two unconnected pads. I hoped this would fix itself when I heated them, but I have plenty of solder wick if not.

Placing the components was repetitious and rather tedious. Fortunately I only have four types of components to place: two transistors with different numbers of leads, and two values of resistors. There's also the occasional capacitor, but there aren't many of them. I think it took about an hour, but I finally I had them all positioned. I fired up the hot air station, took a deep breath, and started in the lower right corner of the board. I don't have an under-the-board pre-heater, so I began by holding the nozzle a bit higher above the board to warm that area, watching to see if any of the components showed signs of blowing off. After a few minutes I lowered the nozzle and watched in fascination as the misshapen blobs of ooze turned into shiny solder joints. I worked my way up the board, allowing the excess heat from the area I was soldering to warm the adjacent areas. Once started the process went surprisingly fast.

One big difference between using hot air and using a soldering iron: the iron heats small spots rather rapidly, while the hot air heats large areas of the board rather slowly. This is especially true for a multi-layer board with large copper planes. Don't try to pick up the board until it cools!

Once the board had cooled enough to handle, I gave it a thorough inspection. I found one joint that hadn't reflowed; a brief touch with an iron fixed that. I could see the solder-stealing effects the via-in-pad technique, where the via had wicked away some of the solder that otherwise would have been on the joint. With 12 mil vias the effect wasn't disastrous, but I could see where it might be a problem with production runs. And those blobs that had run together? They separated out nicely into separate joints with no bridges.

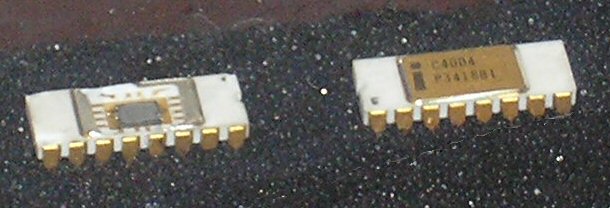

Here's a blurry photo of the result, after I added the large connector and plugged into the test jig:

The smaller connector on the left isn't soldered in place, so I may be able to use the stencil to prep the DRAM array when I get to it; I'm not sure yet. I'll try to take a better picture later this week.